從硅片到軟件 集成電路設計流程中的軟件開發全景解析

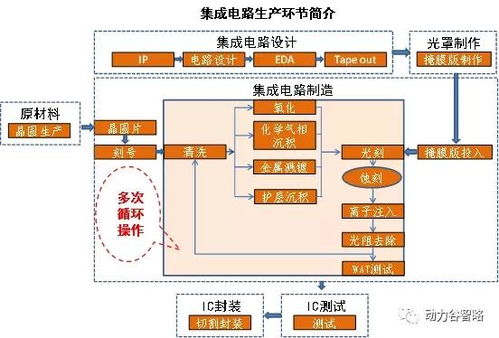

集成電路(IC)設計是一個高度復雜、多階段協同的系統工程,其成功不僅依賴于先進的半導體工藝和精密的物理設計,更離不開貫穿始終、不斷演進的軟件開發工作。現代IC設計流程本質上是“用軟件設計硬件”的過程,軟件開發已深度融入并驅動著每一個環節。

一、 前端設計:算法與架構的軟件實現

- 系統級建模與算法開發:設計始于概念。工程師使用高級建模語言(如SystemC、MATLAB/Simulink、Python)或專用電子系統級(ESL)工具,在軟件環境中構建虛擬原型,進行系統架構探索、性能評估和算法驗證。例如,為了一顆圖像處理芯片,其核心的降噪、壓縮算法首先會在軟件層面實現和優化。

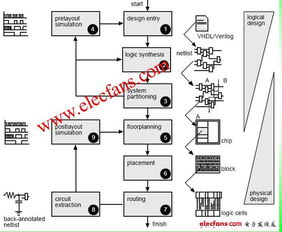

- 硬件描述語言(HDL)編碼與仿真:這是核心的“設計輸入”階段。工程師使用Verilog或VHDL等HDL,以代碼的形式描述數字電路的功能(行為級)或結構(RTL級)。利用仿真軟件(如ModelSim、VCS、NC-Verilog)搭建測試平臺(Testbench),通過運行大量的測試向量,在軟件層面驗證代碼功能的正確性。這個過程高度依賴軟件開發中的驗證方法學,如受約束的隨機測試、斷言檢查、功能覆蓋率收集等。

- 邏輯綜合與形式驗證:RTL代碼完成后,通過綜合工具(如Design Compiler)將其轉換為基于特定工藝庫的門級網表。這個轉換過程本身就是一個復雜的軟件優化過程。之后,使用形式驗證工具,從數學上嚴格證明綜合后的網表與原始的RTL設計在功能上完全等價,替代了部分耗時的仿真。

二、 后端設計:物理實現的軟件驅動

- 物理設計自動化:這是軟件密集型領域。布局布線工具(如Innovus、ICC2)將門級網表轉換成具體的物理版圖。軟件需要自動完成:

- 布局:決定數百萬甚至數十億個標準單元在芯片上的位置。

- 時鐘樹綜合:構建低偏移、低功耗的全局時鐘分布網絡。

- 布線:在多層金屬層上連接所有單元,滿足時序、電學規則。

- 簽核分析:進行靜態時序分析、電源完整性分析、信號完整性分析等,確保設計滿足性能、可靠性和功耗目標。所有這些工具的核心都是極其復雜的算法軟件。

- 設計流程自動化與數據管理:面對海量的設計文件、工具腳本和版本,需要開發或集成強大的流程自動化框架和數據管理系統。這通常涉及Python、Tcl、Perl等腳本語言,用于串聯工具、定制檢查點、生成報告和實現自動化回歸測試,顯著提升設計效率和一致性。

三、 軟硬協同與驗證:軟件開發的關鍵橋梁

- 固件與底層驅動開發:在芯片設計的與之配套的固件(Firmware)和硬件抽象層驅動開發就已啟動。這些軟件直接與芯片寄存器交互,是喚醒芯片、配置功能、實現基礎控制的關鍵。它們通常在虛擬原型或FPGA原型平臺上進行早期開發與驗證。

- 原型驗證與仿真加速:為了更早地運行真實的軟件,會使用FPGA構建硬件仿真平臺,或將設計映射到專用的仿真加速器(如Palladium, ZeBu)。此時,完整的操作系統或應用程序可以在“準芯片”上運行,進行軟硬件聯合調試,發現深層次交互問題。支持這些平臺的軟件工具鏈和調試環境開發至關重要。

四、 支撐環境:軟件開發的基礎設施

- 電子設計自動化工具開發:EDA(電子設計自動化)廠商(如Synopsys, Cadence, Siemens EDA)本身就是頂尖的軟件公司。他們開發的綜合、布局布線、仿真、驗證工具,是IC設計流程的基石,集成了計算機科學、算法優化和芯片物理的最新成果。

- 工藝設計工具包開發:晶圓廠提供的PDK包含工藝文件、標準單元庫、復雜IP的仿真模型等,其中大量的文件(如.lib, .lef, .gds)和配套的驗證規則腳本,都是為EDA工具服務的“軟件數據包”,其質量直接影響設計成敗。

- 內部工具與腳本開發:大型芯片設計公司通常擁有龐大的內部軟件開發團隊,用于開發定制化工具、提升現有工具效率、構建統一的設計平臺和數據分析系統,以形成獨特的設計競爭力。

結論

集成電路設計流程與軟件開發已密不可分。軟件開發不僅是實現設計意圖(前端編碼)和實現物理轉換(后端工具)的手段,更是進行架構探索、功能驗證、性能分析和流程管理的核心驅動力。一顆先進芯片的誕生,是硬件架構師、電路設計師與軟件算法工程師、工具開發工程師、驗證工程師緊密協作的結晶。隨著芯片規模擴大和系統復雜度提升,特別是面向人工智能、自動駕駛等領域的異構計算芯片興起,基于軟件的系統級設計、敏捷開發方法和持續集成/持續驗證的理念,正變得比以往任何時候都更加重要。

如若轉載,請注明出處:http://www.wokaa.cn/product/55.html

更新時間:2026-01-05 09:46:55