模擬集成電路設計精粹 第六章 集成電路設計全覽

在《模擬集成電路設計精粹》的第六章中,作者深入探討了現代集成電路設計的核心思想、設計流程與關鍵權衡。這一章不僅是理論知識的集大成者,也是連接抽象概念與物理實現的橋梁,為工程師提供了從架構規劃到最終版圖的全景式指引。

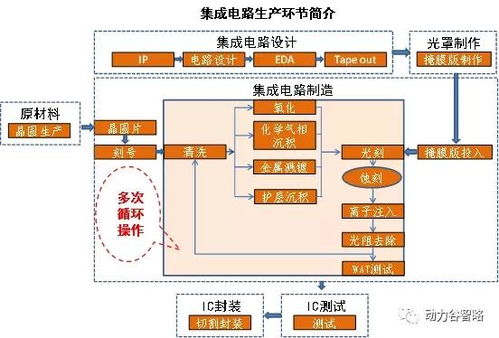

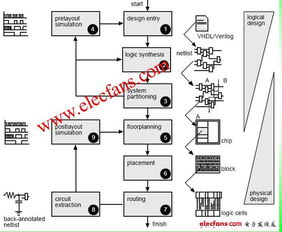

本章開宗明義地強調了集成電路設計的層次化思想。設計并非一蹴而就,而是從系統級規范(Specifications)開始,逐層分解為架構級、電路級、晶體管級乃至版圖級的實現。這種自頂向下的方法(Top-Down Design)確保了設計的可控性與目標一致性,同時輔以自底向上的驗證(Bottom-Up Verification),通過仿真和模型迭代修正,形成完整的設計閉環。層次化設計不僅管理了復雜性,也明晰了各階段的設計目標與驗證標準。

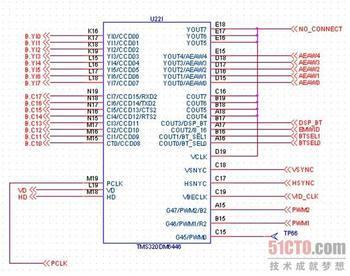

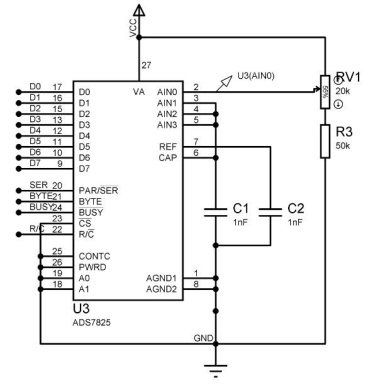

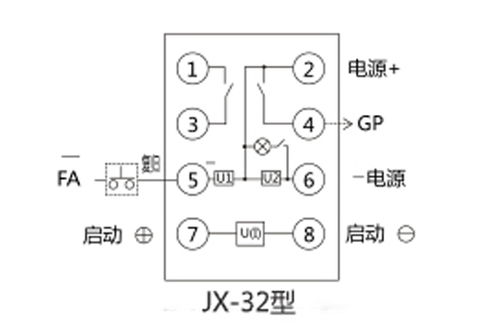

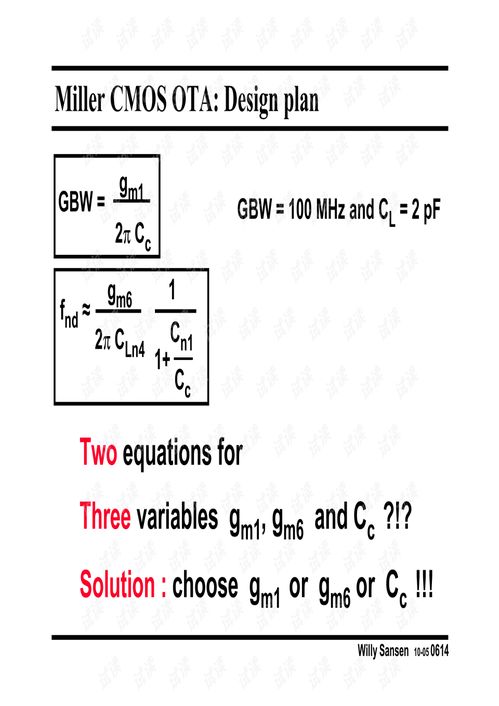

接著,文章聚焦于設計流程的核心環節:電路設計與仿真。在確定系統架構后,設計者需將功能模塊轉化為具體的晶體管級電路。這涉及到深入的器件物理知識,例如MOSFET的工作區域、增益、帶寬、噪聲與功耗特性。設計不再是孤立的參數計算,而是在多重約束下(如增益帶寬積GBW、相位裕度、壓擺率、電源電壓抑制比PSRR)的優化過程。作者通過經典運放(如折疊共源共柵、兩級運放)的設計實例,詳細說明了如何通過手工分析與仿真工具(如SPICE)協同工作,逐步迭代以達到性能指標。這里,折衷(Trade-off)藝術展現得淋漓盡致:速度與精度、功耗與噪聲、面積與成本之間的平衡,是模擬設計永恒的主題。

然后,本章過渡到版圖設計(Layout Design)與物理實現。電路性能的最終保障,極大程度依賴于精心的版圖規劃。作者系統介紹了匹配性設計(如差分對、電流鏡的共質心布局)、寄生效應控制(如減少寄生電容與電阻)、噪聲隔離(如保護環、屏蔽層)以及可靠性考量(如天線效應、閂鎖效應防護)。版圖不僅是幾何圖形的繪制,更是電學特性的物理體現。設計規則檢查(DRC)、電路圖與版圖一致性檢查(LVS)以及后仿真(Post-layout Simulation)構成了確保制造正確性的三重關卡,任何疏忽都可能導致芯片失效或性能劣化。

本章以設計方法論收尾,指出了現代IC設計團隊協作、IP復用以及設計自動化工具(如模擬電路綜合、混合信號驗證)的發展趨勢。盡管工具日益強大,但設計者的洞察力與經驗仍是不可替代的核心。第六章的精髓在于,它將集成電路設計描繪為一個兼具科學嚴謹性與工程創造性的過程:在數學方程與物理定律的框架內,通過巧妙的構思與細致的實現,將抽象創意轉化為硅片上的高性能電路。

總而言之,第六章作為《模擬集成電路設計精粹》的關鍵部分,不僅提供了具體的設計技術與流程知識,更培養了讀者系統化的設計思維。它提醒我們,優秀的模擬IC設計,是在深刻理解基本原理的基礎上,于約束的海洋中精準航行的藝術,每一處細節都關乎最終芯片的靈魂——性能與可靠性。

如若轉載,請注明出處:http://www.wokaa.cn/product/53.html

更新時間:2026-01-05 05:33:13