數字集成電路門控時鐘可靠性研究 關鍵技術與挑戰

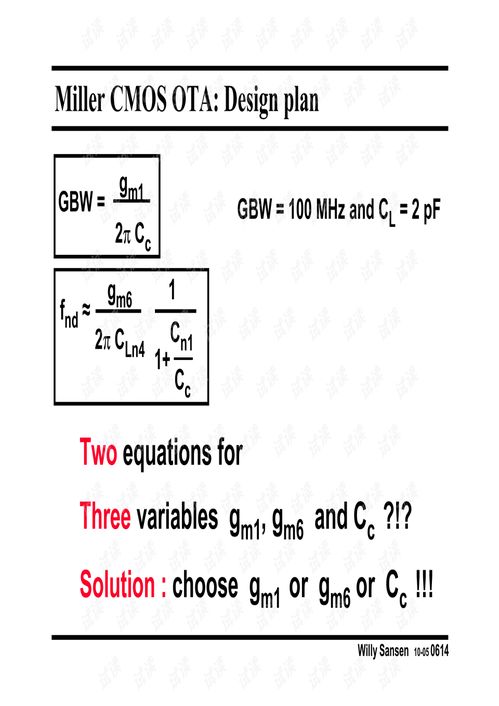

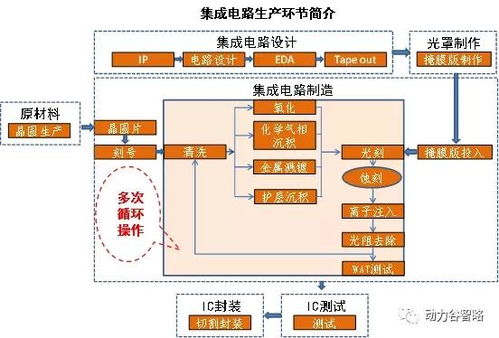

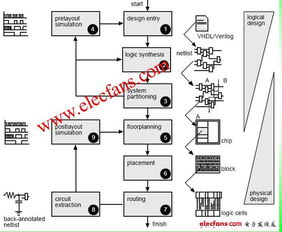

隨著半導體工藝進入納米乃至更先進節點,數字集成電路的功耗、性能和面積(PPA)優化變得日益關鍵。其中,門控時鐘技術作為降低動態功耗最有效的手段之一,被廣泛應用于現代高性能與低功耗芯片設計中。該技術在顯著節省功耗的也引入了復雜的時序、功能及可靠性問題,對集成電路設計的魯棒性提出了嚴峻挑戰。本文旨在系統探討門控時鐘技術的可靠性研究,分析其潛在風險,并綜述當前的主流緩解策略。\n\n### 1. 門控時鐘技術概述與可靠性挑戰\n門控時鐘的基本原理是通過在時鐘路徑中插入邏輯門(通常是“與”門或“或”門),在電路模塊處于空閑狀態時,切斷其時鐘信號,從而消除該模塊中觸發器不必要的翻轉,大幅降低動態功耗。盡管概念簡單,但其實現卻帶來了多方面的可靠性隱患:\n\n- 時序違例風險:插入的門控單元本身會引入額外的延遲,可能惡化時鐘路徑的時序。更關鍵的是,使能信號(Enable)的生成與時鐘信號之間的時序關系必須嚴格滿足建立時間和保持時間要求,否則會導致門控邏輯誤操作,產生毛刺或使能信號與時鐘邊沿競爭,從而造成功能錯誤。\n- 時鐘毛刺與脈沖寬度失真:如果使能信號在時鐘有效沿附近變化,門控邏輯可能輸出一個寬度異常(過窄或過寬)的時鐘脈沖。過窄的脈沖可能導致觸發器無法正確鎖存數據(亞穩態風險增加),過寬的脈沖則可能違反觸發器的最大脈沖寬度限制。\n- 測試與可觀測性困難:門控時鐘結構會阻礙掃描鏈測試中對時鐘的控制,使得故障覆蓋率下降。在功能調試時,時鐘網絡的非連續性也增加了內部狀態觀測的難度。\n- 工藝變異與老化效應:在先進工藝下,工藝、電壓、溫度(PVT)的變異以及晶體管老化(如NBTI、HCI效應)會影響門控單元和使能生成路徑的時序特性,可能使設計在生命周期后期出現原本驗證中未發現的時序失效。\n\n### 2. 提高可靠性的關鍵技術方法\n為確保門控時鐘設計的可靠性,設計流程中需采用一系列綜合性的技術與方法:\n\n1. 安全的門控單元設計與集成:\n - 采用鎖存器型門控時鐘單元(ICG):這是工業界的標準做法。ICG內部集成了一個鎖存器,用于鎖存使能信號,確保使能信號僅在時鐘低電平時變化,從而從根本上避免了時鐘高電平期間的使能信號跳變,消除了產生毛刺的主要根源。\n - 物理設計考量:將ICG單元放置在靠近時鐘根部的層次,并進行謹慎的布局布線,以最小化時鐘偏差(Skew)和插入延遲的影響。對使能信號路徑給予與時鐘網絡類似的時序約束和優化優先級。\n\n2. 嚴謹的靜態時序分析與驗證:\n - 建立多情景、多角點(MCMM)分析:必須對門控時鐘的使能信號路徑進行最嚴格(最大延遲)和最寬松(最小延遲)情況下的時序分析,以同時檢查建立時間和保持時間違例,覆蓋所有PVT和老化場景。\n - 時鐘門控檢查:使用EDA工具專門的時鐘門控檢查功能,驗證使能信號與時鐘之間的時序關系是否符合ICG單元的要求,并檢查是否存在非預期的門控邏輯。\n\n3. 可測試性設計集成:\n - 測試模式下的門控旁路:在掃描測試模式下,通過額外的測試控制信號(如Test\_Mode)強制使所有門控單元處于“常開”狀態,恢復完整的時鐘網絡,確保測試向量能夠正常加載和捕獲。\n - 內建自測試支持:設計需考慮BIST邏輯的時鐘需求,確保在BIST運行時,相關模塊的時鐘門控處于受控狀態。\n\n4. 動態電壓與頻率縮放協同設計:\n - 在采用DVFS的系統中,電壓和頻率的變化會直接影響時序余量。門控時鐘的使能生成邏輯必須被設計為能在所有工作電壓和頻率點下都保持安全,通常在模式切換時需要安排安全的時鐘停頓時序。\n\n### 3. 未來展望與結論\n面向未來更先進的工藝和更復雜的應用(如人工智能加速器、自動駕駛芯片),門控時鐘技術將繼續演進。細粒度門控、基于數據流的自適應門控等高級技術能帶來更大的功耗收益,但其可靠性設計也更為復雜。機器學習方法開始被應用于預測最佳的門控策略和識別潛在的時序風險點。硅后驗證與監控技術,如利用片上傳感器監測時鐘脈沖寬度和延遲,將為可靠性保障提供閉環反饋。\n\n總而言之,門控時鐘是一把“雙刃劍”。成功的集成電路設計必須在追求極致功耗效率與確保系統絕對可靠之間取得精妙平衡。這要求設計工程師不僅深入理解電路原理和EDA工具,更需在整個設計周期——從架構規劃、RTL編碼、綜合、布局布線到簽核驗證——中,將可靠性作為一項核心指標進行持續評估與優化。唯有通過系統性的方法和嚴格的設計實踐,才能充分發揮門控時鐘的節能潛力,同時構建出堅實可靠的數字集成電路系統。

如若轉載,請注明出處:http://www.wokaa.cn/product/49.html

更新時間:2026-01-05 06:15:28