集成電路中的時(shí)延可測(cè)性設(shè)計(jì)

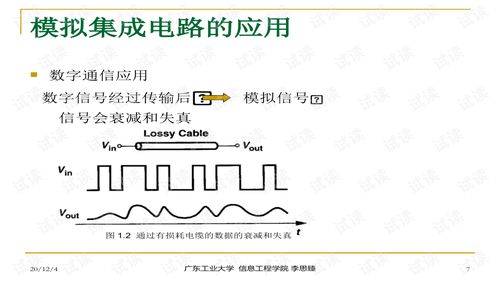

在現(xiàn)代集成電路(IC)設(shè)計(jì)與制造中,時(shí)延可測(cè)性設(shè)計(jì)(Delay Testability Design)已成為確保芯片性能可靠性的關(guān)鍵環(huán)節(jié)。隨著半導(dǎo)體工藝不斷向納米級(jí)演進(jìn),電路時(shí)延問(wèn)題日益突出,直接影響到芯片的工作頻率、功耗和整體功能。時(shí)延可測(cè)性設(shè)計(jì)通過(guò)嵌入特定的測(cè)試結(jié)構(gòu)和機(jī)制,使設(shè)計(jì)師能夠準(zhǔn)確測(cè)量和驗(yàn)證電路中的路徑時(shí)延,從而及早發(fā)現(xiàn)制造缺陷或設(shè)計(jì)偏差。

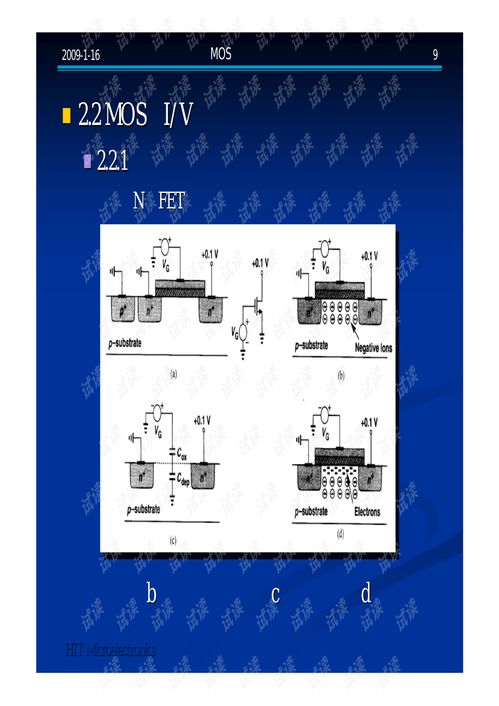

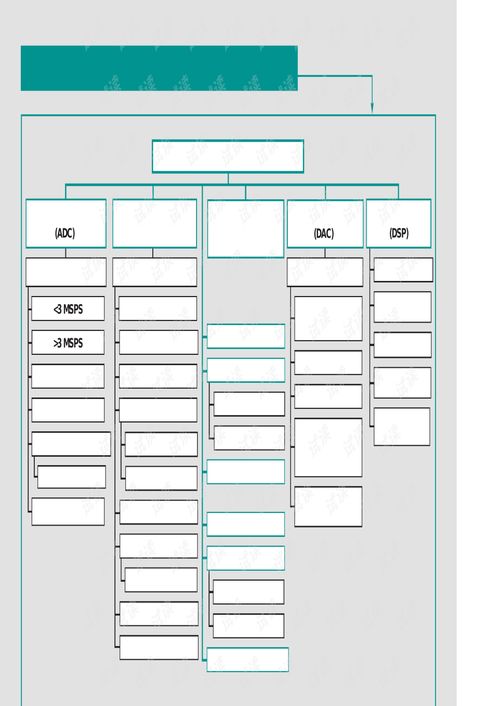

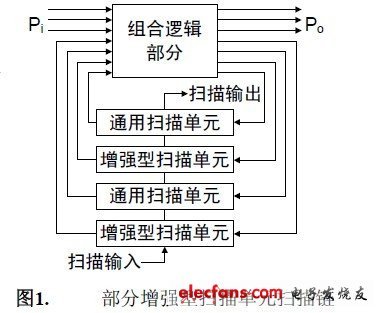

時(shí)延故障通常源于制造過(guò)程中的物理變異,如線(xiàn)寬變化、介電層厚度不均或晶體管參數(shù)漂移。這些因素可能導(dǎo)致信號(hào)在特定路徑上傳播過(guò)慢,進(jìn)而引發(fā)時(shí)序違規(guī),甚至功能失效。為了應(yīng)對(duì)這一挑戰(zhàn),時(shí)延可測(cè)性設(shè)計(jì)采用了多種技術(shù),包括但不限于掃描鏈插入、內(nèi)置自測(cè)試(BIST)和路徑時(shí)延測(cè)試模式生成。例如,通過(guò)將觸發(fā)器配置為掃描單元,測(cè)試人員可以在不同頻率下應(yīng)用測(cè)試向量,捕獲電路響應(yīng),并分析時(shí)延分布。

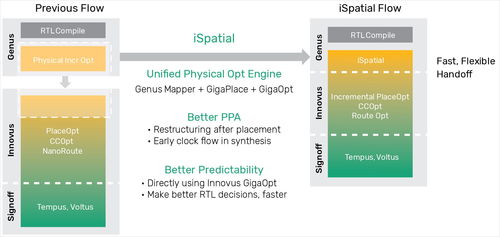

在電子電路圖設(shè)計(jì)階段,時(shí)延可測(cè)性需從架構(gòu)層面集成。設(shè)計(jì)師必須在電路圖中明確標(biāo)識(shí)關(guān)鍵時(shí)序路徑,并添加測(cè)試點(diǎn)或冗余邏輯以支持時(shí)延測(cè)量。這通常涉及使用電子設(shè)計(jì)自動(dòng)化(EDA)工具進(jìn)行靜態(tài)時(shí)序分析(STA)和故障模擬。電子技術(shù)資料網(wǎng)站和在線(xiàn)資源庫(kù)為此提供了豐富的參考設(shè)計(jì)、標(biāo)準(zhǔn)單元庫(kù)和測(cè)試協(xié)議,幫助工程師快速實(shí)現(xiàn)可測(cè)性特性。

軟件開(kāi)發(fā)在時(shí)延可測(cè)性設(shè)計(jì)中扮演著支撐角色。從測(cè)試算法開(kāi)發(fā)到自動(dòng)化測(cè)試模式生成(ATPG)軟件,再到數(shù)據(jù)分析和可視化工具,軟件解決方案極大地提升了測(cè)試效率和覆蓋率。例如,專(zhuān)用軟件可以模擬不同工藝角下的時(shí)延行為,生成優(yōu)化的測(cè)試序列,并與硬件描述語(yǔ)言(如Verilog或VHDL)無(wú)縫集成。開(kāi)源平臺(tái)和商業(yè)軟件包(如Synopsys或Cadence的工具鏈)促進(jìn)了設(shè)計(jì)流程的標(biāo)準(zhǔn)化。

時(shí)延可測(cè)性設(shè)計(jì)是集成電路高可靠性的基石。它結(jié)合了硬件設(shè)計(jì)、軟件工具和電子技術(shù)資源,確保芯片在高速運(yùn)行時(shí)維持穩(wěn)定的性能。隨著人工智能和物聯(lián)網(wǎng)設(shè)備的普及,對(duì)低時(shí)延、高測(cè)試覆蓋的需求將進(jìn)一步加強(qiáng)這一領(lǐng)域的發(fā)展。設(shè)計(jì)師和開(kāi)發(fā)者應(yīng)持續(xù)關(guān)注最新技術(shù)動(dòng)態(tài),利用電子電路圖和軟件開(kāi)發(fā)資源,優(yōu)化可測(cè)性策略,以應(yīng)對(duì)未來(lái)芯片復(fù)雜性的挑戰(zhàn)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.wokaa.cn/product/5.html

更新時(shí)間:2026-01-07 10:30:52